[kembali]

mengetahui dan memahami tentang Binary ripple counter

dapat membuat rangkaian yang terdapat binary ripple counter

2. Pembahasan

[kembali]

Gerbang logika hanya mampu mengubah

sinyal keluaran sejalan dengan sinyal masukan. Bagaimana bentuk ragam

gelombang dari perubahan sinyal tersebut tergantung pada gerbang

logikanya.

Prinsip dasar dari gerbang logika dan kombinasional adalah perubahan

keadaan level keluaran tergantung dari keadaan masukan, untuk setiap

saat dari waktu ke waktu. Jika setiap keadaan masukan berubah maka

gerbang logika akan berubah pula kaluarannya saat itu juga. Jadi

rangkaian gerbang logika hanya berfungsi menyiapkan suatu operasi logika

kemudian hasil dinyatakan pada keluaran.

Pada contoh diatas dapat dilihat kedua

sinyal yang masuk pada gerbang nor saat itu juga diberikan keluarannya

yang terdiri atas satu sinyal.

Dengan membuat gerbang logika

kombinasional kita dapat membuat rangkaian yang dapat menyimpan data.

Rangkaian inilah yang disebut rangkaian Flip Flop. Fliop Flop merupakan

piranti yang dapat menyimpan 1 bit data yaitu 1 atau 0.

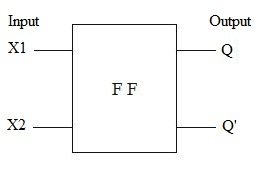

Lambang dan Notasi

Terdapat berbagai jenis flip flop, masing

masing flip flop memmiliki lambang dan notasi yang berbeda. Tetapi

semuanya memiliki dasar lambang yang sama yaitu sebuah kotak dangan

garis depan yang berupa input dan garis belakang yang berupa output

sedangkan kotak merupakan rangkaian flip flop.

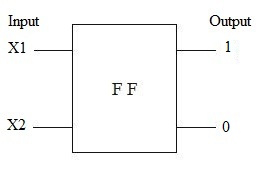

Gambar tersebut menunjukkan dua keluaran

yang di wakili huruf Q dan Q’ yang mana nilai Q’ selalu terbalik

terhadap Q, dua sinyal masukan yang diwakili huruf X1 dan X2, dan kotak

ditengah yang diberi huruf FF merupakan rangkaian flip flop.

Seperti pada gambar diatas, keluaran Q bernilai 1 maka Q’ yang dihasilkan adalah 0

Flip Flop JK

Flip flop JK merupakan flip flop yang paling ideal digunakan sebagai piranti penyikpanan (memori).

Flip flop JK digunakan pada setiap

komputer digital maupun piranti lainnya. Dalam pemakaian bidang

elektronika juga memiliki banyak manfaat, misalnya :

- Pencacah frekuensi (frequency counter)

- Pembagi frekuensi (frequency divider)

- Pembangkit ragam gelombang kotak simetri (symetri square wave form generator), dll.

Flip Flop JK dengan Pemicuan Tepi (Edge Triggered JK Flip Flop)

Rangkaian dari flip flop ini terdiri dari

rangkaian gerbang logika, seperti flip flop lain. Tetapi, flip flop JK

memilki keunikan tersendiri, yaitu pada keluaran Q dan Q’ terdapat dua

jenis umpan balik, dengan keluaran yang diumpan balikkan kembali.

Ada dua jenis umpan balik :

-

Umpan Balik flip flop. Berfungsi supaya rangkaian gerbang logika yang berada di dalam garis putus – putus FL dapat menahan sebuah data biner.

-

Umpan balik Togel (Toggle). Umpan balik ini enyebabkan flip flop JK mengalami toggle.

Selain terdapt dua jenis umpan balik,

flip flop JK memiliki 2 masukan kendali, yang disebut dengan masukan J

dan K. Masukan J dan K berfungsi mengatur apa yang akan dilakukan

rangkaian pada tepi sinyal pendetak. pada bagian masukan dari pendetak

dibei rangkaian Diferensator, namun dalam Chip IC tidak digunakan

rangkaian RC tetapi gerbang Not dan And, karena pada IC, komponen RC

memakan Tempat dan kurang praktis.

Diagram blok Flip FLop JK Pemicuan Tepi

Rangkaian Sesungghnya Flip FLop JK Pemicuan Tepi

Tabel Kebenaran

Pinsip Kerja Flip Flop JK

-

Keadaan tidak Aktif.Diagram Masukan

Ini adalah keadaan dimana sinyal J dan K bernilai 0 sehingga juga menghasilkan masukan Q bernilai 0 -

Keadaan SET.Diagram Masukan

Ini terjadi disaat sinyal pada masukan J bernilai 1 dan masukan K bernilai 0 sehingga dihasilkan keluaran Q bernilai 1, pada saat ini lah Flip Flop dinyatakan dalam keadaan SET -

Keadaan RESET.Diagram Masukan

Ini terjadi disaat sinyal pada masukan J bernilai 0 dan masukan K bernilai 1 sehingga dihasilkan keluaran Q bernilai 0, pada saat ini lah Flip Flop dinyatakan dalam keadaan RESET -

Keadaan Toggle.Diagram Masukan

Ini terjadi saat masukan J dan K sama sama berniali 1 sehingga dihasilkan keadaan set dan reset yang terus bergantian

Flip Flop JK dengan Pemicuan Tepi Negatif

Flip Flop JK dengan Pemicuan Tepi Negatif

memiliki prinsip kerja yang sama dengan tipe sebelumnya, yang berbeda

hanya pada pemicu yang digunakan saling berlawanan. Biasanya data yang

diterima adalah perubahan pulsa ke rendah (tepi negatif), cara pemasukan

data J dan K seperti ini dibuat dengan merancang flip flop agar emiliki

kemampuan untuk dapat menerima data masukan kendali masukan J dan K

dari tepi sinyal pendetak.

Tabel Kebenaran

Flip Flop JK pemicuan Tepi Negatif

Flip Flop JK MS

Ciri khusus Flip Flop JK MS (master-slave)

Flip Flop JK MS menjadi seri terbaik dari

Flip Flop dikarenakan memiliki 2 masukan sinyal kendali Asinkron S dan

R, flip flop JK MS dapat dikendalikan dengan 3 mode operasi yaitu

sinkron, asikron, dan kombinasi sinkron dan asinkron Rangkaian Flip Flip

JK MS juga memiliki 3 jenis umpan balik

Ada 3 jenis umpan balik, yaitu :

-

Umpan Balik flip flop bagian Master. Ini berfungsi agar rangkaian gerbang logika yang berada dalam bagian master dapat menahan sebuah data biner.

-

Umpan balik flip flop bagian Slave. Sama halnya dangan bagian Master, gerbang logika pada Salve juga berfungsi untuk menahan data pada bagiannya

-

Umpan balik Togglel. Umpan balik ini menyebabkan flip flop JK

- Saat sinyal detak pada tingkat tinggi, majikan aktif dak budak tidak aktif

- Saat sinyal detak pada tingkat rendah, majikan menjadi tidak aktif dan budaknya menjadi aktif

- Apa yang dilakukan Majikan akan diikuti oleh Budak, dan apa yang dilakukan oleh Budak tidak diikuti oleh Majikan.

Prinsip Kerja Flip Flop JK MS

- Keadaan Tak Aktif

Diagram Masukan

Dinyatakan tidak aktif (tidak bekerja) apabila pada smua masukannya, yaitu SET, RESET, J dan K tidak terdapat sinyal masuk. Walaupun sinyal pendetak terus berdenyut flip flop tidak akan bereaksi, dan keluaran Q dalam keadaan kosong. - Keadaan Set

Diagram Masukan

Langkah pertama yaitu membuat flip flop dalam keadaan SET. Caranya , masukkan SET diberi sinyal, atau dibuat masukan SET dalam keadaan 1. Keluaran Q saat diubah menjadi SET flip fliop tidak langsung SET, tetapi menunggu terlebih dahulu datangnya sinyal pendetak. Itupun baru akan bekerja setelah sinyal pendetak berubah keadaannya dari positif ke negatif. - Keadaan RESET

Diagram Masukan

Jika bagian Budak Set dengan cara membuat masukan kendali aktif (1), maka flip flop dalam keadaan aktif dan cara memadamkannyad dilakukan dengan mengaktifkan masukan sinyal kendali K, setelah mana flip flop akan berubah menjadi tak aktif. Jika masukan kendali K diaktifkan, maka flip flop tidak akan langsung padam tetapi menunggu terlebih dahulu sinyal pendetak. Sewaktu sinyal pemdetak ada, flip flop akan menunggu sampai tepi negatif terjadi. - Keadaan TOGGLE

Diagram Masukan

Bila masukan J dan K tinggi, bagian master akan mengalami Toggle satu kali ketika sinyal pendetak tinggi. Bagian slave juga akan mengalami Toggle satu kali sinyal pendetak rendah. Intinya, apapun yang dilakukan oleh Master akan selalu diikuti oleh Slave. Pada keadaan ini keluaran Q dan Q’ akan berkedip-kedip secara bergantian. Kecepatannya lebih lambat separuhnya dari kecepatan sinyal pendetak, atau dapat dikatakan bahwa frekuensi keluaran Q sewaktu Toggle lebih kecil setengahnya dibanding sinyal pendetak Clk. Flip flop JK MS dirancang untuk bekerja dalam keadaaan Toggle. Dengan begitu flip flop dengan sendirinya akan membagi frekuensi sinyal pendetak menjasi etengahnya. - Keadaan PRESET

Diagram Masukan

Dalam pengoperasionalkan flip flop JK MS, diperlukan penginterupsian. Dapat dilakukan untuk mengambil alih operasi flip flop. Contohnya, saat SET dengan CLEAR dapat mengubah flip flop yang RESET menjadi SET.Pengambil alihan ini disebut Operasi Asinkron atau tidak serempak. Masukan Kendali preset dapat langsung ditanggapi oleh flip flop, dan saat itu juga keluaran Q akan langsung aktif. Flip Flop akan menjadi Set - Keadaan CLEAR

Diagram Masukan

Masukan Clear dapat mengubah flip flop menjadi RESET. Masukan Clear akan langsung ditanggapi tanpa harus menunggu sinyal pendetak. Flip flop akan langsung berubah menjadi Reset. Keluaran Q akan tidak aktif. Masukan kendali Preset dan Clear tidak perlu menunggu datangnya sinyal pendetak, sehingga mode operasinya disebut asinkron.

Rangkaian Sesungguhnya Flip Flop JK MS

Flip Flop 7475 dan Flip Flop 74LS76

adalah IC JK MS yang sangat terkenal karena terdapat dua flip flop JK

MS, dan mempunyai masukan asinkron (Rd dan Sd0, masukan sinyal pendetak

Clk pemicuan tepi dan masukan sinkron sinyal kendali J dan K. IC TTL

7476 adalah sebuah pemicuan tepi pendetak pulsa positif, sedangkan flip

flop JK MS 74LS76 adalah pemicuan tepi pendetak pulsa negatif.

Tabel Kebenaran IC Flip Flop JK MS

Dari gambar dan tabel, dapat dilihat

bahwa masukan asinkron Sd dan Rd adalah aktif rendah, artinya suatu

keadaan Low atau 0 pada Sd akan membuat flip flop menjadi Set (Q=1) dan

suatu keadaan Rd akan menyebabkan flip flop menjadi Reset (Q=0).Secara

keseluaruhan dapat dilihat bahwa flip flop JK MS tidak hanya berfungsi

sebagai penyimpan data biner, tetapi juga dapat mengendalikan isi data

biner tersebut dengan berbagai cara.

Sistem Dinamik-

Masukan Statik. Masukan dengan tanda (——) diartikan sebagi flip flop atau rangkaian digital bersifat statik, artinyatidak menggnakan sinyal pendetak. Masukan dengan tanda (——o) diartikan sebagai masukan negatif flip flop atau rangkaian digital bersifat statik artinya tidak menggunakan sinyal pendetak.

-

Masukan Dinamik. Masukan dengan tanda (—->) diartikan sebagai masukan dinamik flip flop atau rangkaian digital bersifat dinamik, artinya menggunakan sinyal penggerak. Masukan dengan tanda (—-o>) diartikan sebagai masukan negatif dinamik flip flop atau rangkaian digital bersifat dinamik, artinya menggunakan sinyal pendetak.Penghitung riak biner N-flip-flop dapat dimodifikasi, untuk memiliki modulus lain kurang dari 2N dengan bantuan logika kombinasional sederhana yang terhubung secara eksternal. Kami akan mengilustrasikan konsep sederhana ini dengan bantuan contoh. Pertimbangkan pengaturan penghitung riak biner empat-flip-flop dari Gambar 11.3 (a). Ini menggunakan J-K flip flop dengan input CLEAR asinkron RENDAH aktif. Gerbang NAND pada gambar memiliki output yang terhubung ke input CLEAR dari keempat flip-flop. Input untuk gerbang NAND tiga input ini berasal dari Q output dari sandal jepit FF0, FF1 dan FF2. Jika kita mengabaikan gerbang NAND selama beberapa waktu, penghitung ini akan melalui urutan biner alami dari 0000 hingga 1111. Tetapi itu tidak terjadi di masa sekarang pengaturan. Penghitung mulai menghitung dari 0000 ke penghitungan akhir 1111. Penghitung terus menghitung selama input CLEAR asinkron dari flip-flop yang berbeda tidak aktif. Bahwa adalah, output gerbang NAND adalah TINGGI. Ini adalah kasus sampai penghitung mencapai 0110. Dengan ketujuh clock pulse cenderung menuju ke 0111, yang membuat semua input gerbang NAND menjadi TINGGI, memaksa outputnya ke RENDAH. Transisi TINGGI ke RENDAH ini pada output gerbang NAND membersihkan semua output flip-flop ke logika ‘Menyatakan 0, sehingga melarang penghitung untuk menetap di 0111. Dari pulsa jam kedelapan dan seterusnya, counter mengulangi urutannya. Penghitung selalu dihitung dari 0000 hingga 0110 dan kembali ke 0000. Sembilan negara sisanya, yang meliputi 0111, 1000, 1001, 1010, 1011, 1100, 1101, 1110 dan 1111, dilewati, dengan hasil kita mendapatkan penghitung MOD-7

Pada bagian ini, kita akan melihat diagram logika internal penghitung riak biner yang umum dan melihat caranya tutup arsitekturnya adalah ke konter riak yang dijelaskan di bagian sebelumnya. Mari kita pertimbangkan biner ripple counter type number 74293. Ini adalah counter ripple biner empat bit yang berisi empat flip-flop J-K tipe master-slave dengan gating tambahan untuk menyediakan penghitung pembagian-oleh-2 dan tiga-tahap MOD-8 melawan. Gambar 11.4 menunjukkan diagram logika internal penghitung ini. Untuk mendapatkan urutan biner penuh dari 16 negara, output Q dari flip-flop LSB terhubung ke input B, yang merupakan input jam dari flip-flop berikutnya yang lebih tinggi. Pengaturan kemudian menjadi sama seperti yang ditunjukkan pada Gambar. 11.2 (a), dengan pengecualian gerbang NAND dua-input pada Gambar 11.4, yang telah disertakan di sini untuk penyediaan fitur kliring. Penghitung dapat dihapus ke keadaan logika 0000 dengan mengarahkan kedua input RESET ke keadaan logika TINGGI. Tabel 11.2 dan 11.3 masing-masing memberikan tabel fungsional dan urutan hitungan.

• Penghitung dihitung dalam urutan alami dari 0000 hingga 1011.• Saat penghitung masuk ke 1100, output NAND pergi ke keadaan logika ‘0’ dan segera membersihkan konter ke kondisi 0000.• Dengan demikian, penghitung tidak dapat tetap dalam kondisi 1100. Ini hanya memiliki 12 kondisi stabil dari 0000 hingga 1011.• Oleh karena itu, modulus penghitung = 12.• Output Q3 adalah frekuensi jam input dibagi dengan 12.• Oleh karena itu, frekuensi gelombang output Q3 = 1.2 × 103/12 = 100 kHzBIN

[kembali]

- Negative Edge-Triggered J-K flip-flops

Pada JK flip-flop dibuat jalur balik

dari masing-masing keluaran Q dan Q’ menuju gerbang masukan NAND, hal ini

tidak masalah karena gerbang NAND dapat memiliki lebih dari dua masukan.

Nama JK flip-flop diambil untuk membedakan dengan masukan pada SR

flip-flop karena ada perubahan ada perubahan jalur balik di atas. Secara umum

cara kerja JK flip-flop sama dengan SR flip-flop. Perbedaannya pada saat JK

bernilai 1 1 yang menyebabkan kondisi keluaran berubah (1 ke 0 dan 0 ke 1) atau

toggle.

JK flip-flop memiliki 2 masukan yang biasanya ditandai dengan huruf J dan

K. Jika J dan K berbeda maka keluaran Q akan sama dengan nilai J pada clock

berikutnya (next clock). Jika J dan K keduanya 0 maka tidak terjadi perubahan

apa-apa pada flip-flop. Jika J dan K keduanya 1 maka kondisi Q akan berubah dari

kondisi sebelumnya, Jika sebelumnya Q bernilai 0 maka akan bernilai 1 dan

sebaliknya.

Karakter JK flip-flop yang lebih pasti untuk semua kondisi maka flip-flop

ini yang banyak digunakan untuk membangun berbagai komponen register

seperti: register geser (shift register), pencacah biner (binary counter),

pendeteksian sekuensial (sequence detector) dan lain-lain.

Pada saat clock naik/bernilai 1 maka kondisi keluaran Q ditentukan oleh

masukan JK. Kondisi Set (keluaran bernilai 1) tercapai pada saat JK bernilai 10.

Kondisi Reset (keluaran bernilai 1) tercapai pada saat JK bernilai 01. Pada flip flop

JK tidak ada lagi kondisi pacu seperti pada flip-flop SR. Pada saat JK bernilai 11

maka nilai keluaran Q akan berubah-ubah (toggle) pada saat setiap clock -nya.

tabel kebenaran JK Flip flop

2. Clock (detak)

lock yaitu pulsa-pulsa periodik yang biasanya berbentuk bujur sangkar

(duty cycle 50%), seperti yang ditunjukkan pada gambar 16. SR Flip-Flop bekerja

secara asinkron. Nilai S dan R dapat berubah kapan saja dan dalam tempo yang

tidak bersamaan. Detak (clock) ditambahkan pada sisi masukan untuk menjaga

sinyal agar bekerja dalam tenggang tempo yang bersamaan.

Operasi-operasi yang terjadi di dalam sistem digital sinkron terjadi pada

waktu-waktu pulsa clock bertransisi dari 0 ke 1 atau dari 1 ke 0. Waktu-waktu

transisi ini ditunjukkan pada gambar 16. Transisi 0 ke 1 disebut sisi naik (rising

edge) atau sisi menuju positif, transisi dari 1-ke-0 disebut sisi jatuh (falling edge)

atau sisi menuju negatif.

Kendali ini membantu flip-flop lebih stabil. Clock ditambahkan sebelum

sinyal S dan R masuk ke dalam rangkaian flip-flop. Masing-masing sinyal masukan

di NAND-kan dengan clock. Pada saat clock bernilai 0, tidak ada perubahan sinyal

yang masuk ke dalam flip-flop.

3. Logicstate

untuk memberikan nilai logika 1 atau 0

4. Logicprobe

untuk menampilkan nilai keluaran, yang nilainya 0 atau 1.

5. Gerbang NAND

menampilan nilai inverter dari input gerbang AND.

4. Percobaan

[kembali]

a. Fig. 11.2

Prinsip kerja :

Rangkaian akan aktif ketika logika input adalah 1. Ketika logika input 1 maka fungsi penghitung sebagai berikut. Mari kita asumsikan bahwa semua flip flop pada awalnya dihapus ke kondisi '0'. Pada transisi TINGGI ke RENDAH dari pulsa jam pertama, Q0 beralih dari ‘0’ ke ‘1 ow karena tindakan bergantian. Karena flip flop yang digunakan adalah yang dipicu oleh negatif edge, transisi '0' ke '1' pada Q0 tidak memicu flip-flop FF1. FF1, bersama dengan FF2 dan FF3, tetap dalam kondisi '0'. Jadi, pada terjadinya transisi clock negative-going pertama, Q0 = 1, Q1 = 0, Q2 = 0 dan Q3 = 0. Pada transisi TINGGI ke RENDAH dari pulsa clock kedua, Q0 beralih lagi. Artinya, mulai dari ‘1’ hingga ‘0’. Transisi '1' ke '0' pada output Q0 memicu FF1, output Q1 yang berasal dari '0' ke ‘1’. Output Q2 dan Q3 tetap tidak terpengaruh. Oleh karena itu, segera setelah terjadinya transisi TINGGI ke RENDAH kedua dari sinyal clock, Q0 = 0, Q1 = 1, Q2 = 0 dan Q3 = 0. Pada baris yang sama, kita dapat menjelaskan status logika Q0, Q1 , Output Q2 dan Q3 segera setelah transisi jam berikutnya. Status logika output untuk 16 pertama transisi sinyal jam relevan (TINGGI ke RENDAH) dirangkum dalam Tabel 11.1. Dengan demikian, kita melihat bahwa penghitung melewati 16 keadaan yang berbeda dari 0000 ke 1111 dan kemudian, pada terjadinya transisi yang diinginkan dari pulsa clock keenambelas, ia me-reset ke keadaan asli 0000 dari tempat dimulainya. Hal ini sesuai dengan tabel kebenaran.

b. Fig. 11.3

Prinsip Kerja :

Rangkaian ini menggunakan J-K flip-flop dengan tidak aktifLOWsinkronkan CLEARinput. NANDmembukintidakmenentukanoutput yang terhubung dengan input CLEAR dari keempat flip-flop. Input ke gerbang NAND tiga input ini berasal dari output Q dari flip-flop FF0, FF1 dan FF2. Jika kita mengabaikan gerbang NAND untuk beberapa waktu, penghitung ini akan melalui urutan biner alami dari 0000 hingga 1111. Tetapi itu tidak terjadi dalam pengaturan saat ini. Penghitung mulai menghitung dari 0000 ke penghitungan akhir 1111. Penghitung terus menghitung selama input CLEAR asinkron dari flip flop berbeda tidak aktif. Artinya, output gerbang NAND adalah TINGGI. Ini adalah kasus sampai penghitung mencapai 0110. Dengan pulsa jam ketujuh ia cenderung pergi ke 0111, yang membuat semua gerbang NAND input TINGGI, memaksa outputnya ke RENDAH. Transisi TINGGI ke RENDAH ini pada output gerbang NAND membersihkan semua output flip-flop ke keadaan logika '0', sehingga tidak memungkinkan penghitung untuk diselesaikan pada 0111. Dari pulsa jam kedelapan dan seterusnya, penghitung mengulangi urutannya. Penghitung dengan demikian selalu dihitung dari 0000 hingga 0110 dan kembali ke 0000. Sembilan negara sisanya, yang meliputi 0111, 1000, 1001, 1010, 1011, 1100, 1101, 1110 dan 1111 dilewati, dengan hasil bahwa kita mendapatkan Penghitung MOD-7. Gambar 11.3 (b) menunjukkan bentuk gelombang waktu untuk penghitung ini. Dengan memilih input NAND yang sesuai, seseorang dapat memperoleh penghitung dengan nomor MOD apa pun yang kurang dari 16. Pemeriksaan bentuk gelombang waktu juga mengungkapkan bahwa frekuensi output Q2 adalah 1/7 dari frekuensi clock input. Bentuk gelombang pada output Q2, bagaimanapun, tidak simetris seperti yang akan terjadi jika penghitung akan melalui urutan biner penuh. Output Q3 tetap dalam kondisi logika RENDAH. Diharapkan demikian karena penghitung MOD-7 membutuhkan minimal tiga flip flop. Itulah sebabnya flip-flop keempat, yang seharusnya beralih pada transisi TINGGI ke RENDAH dari pulsa clock kedelapan, dan pada setiap pulsa kedelapan berturut-turut sesudahnya, tidak pernah sampai ke tahap itu. Penghitung dihapus pada pulsa clock ketujuh dan setiap pulsa clock ketujuh berturut-turut sesudahnya. Sebagai ilustrasi lain, jika gerbang NAND yang digunakan dalam pengaturan penghitung pada Gambar 11.3 (a) adalah NAND dua-input dan inputnya berasal dari output Q1 dan Q3, penghitung akan melewati 0000 hingga 1001 dan kemudian mengatur ulang ke 0000 lagi, karena, saat penghitung cenderung beralih dari kondisi 1001 ke kondisi 1010, gerbang NAND beralih dari status '1' ke status '0', membersihkan semua flip flop ke status '0'.

c. Fig. 11.4

Penghitung dihitung dalam urutan alami dari 0000 hingga 1011.

Saat penghitung masuk ke 1100, output NAND pergi ke keadaan logika '0' dan segera membersihkan penghitung ke keadaan 0000.

Dengan demikian, penghitung tidak dapat tetap berada di negara bagian 1100. Hanya memiliki 12 status stabil dari 0000 hingga 1011. Oleh karena itu, modulus penghitung = 12.

Output Q3 adalah frekuensi input jam dibagi 12.

Oleh karena itu, frekuensi gelombang output Q3 = 1.2 × 103/12 = 100 kHz

d. Example 11.3 (fig. 11.5)

soal : Lihat counter riak biner dari Gambar 11.5. Tentukan modulus konter dan juga frekuensi output Q3 flip-flop.

prinsip kerja :

Ketika input berlogika 1, maka sepanjang waktu gelombang pada flip flop JK 1 akan menggambarkan sinyal normal, sedangkan pada flip flop 2, 3, 4 terhubung ke gerbang NAND,

e. Example 11.4 (fig. 11.6)

soal : Rancang penghitung riak biner yang menghitung 000 dan 111 dan lompati enam status yang tersisa, yaitu, 001, 010, 011, 100, 101 dan 110. Gunakan flip flop JK yang dipicu oleh tepi negatif yang dipicu oleh tepi rendah PRESET dan CLEAR yang aktif input. Juga, gambarkan bentuk gelombang pewaktuan dan tentukan frekuensi dari keluaran flip-flop yang berbeda untuk frekuensi clock yang diberikan, fc.

Prinsip kerja :

Penghitung diharuskan untuk pergi ke negara bagian 111 dari negara bagian 000 dengan transisi jam relevan pertama. Transisi kedua membawanya kembali ke status 000. Yaitu, tiga flip flop beralih dari keadaan logika '0' ke keadaan logika '1' dengan setiap transisi jam bernomor ganjil, dan juga tiga flip flop beralih dari keadaan logika '1' ke keadaan logika '0' dengan setiap transisi jam genap. Gambar 11.6 (a) menunjukkan pengaturan. Input PRESET dari ketiga flip-flop telah dikaitkan dengan output NAND yang inputnya QA QB dan QC Setiap kali penghitung berada dalam status 000 dan clock, output NAND sejenak beralih dari status logika '1' ke status keadaan logika '0', dengan demikian mengatur QA QB dan keluaran QC ke keadaan logika '1'. Bentuk gelombang QA, QB dan QC identik, dan masing-masing memiliki frekuensi fc / 2, di mana fc adalah frekuensi clock.

f. Example 11.5 ( fig. 11.7)

soal : Lihat pengaturan penghitung riak biner dari Gambar 11.7. Tulis urutan hitungannya jika awalnya dalam kondisi 0000. Juga menggambar gelombang waktu.

Prinsip Kerja :

Penghitung awalnya dalam kondisi 0000. Dengan pulsa jam pertama, Q0 beralih dari '0' ke '1', yang berarti Q0 beralih dari '1' ke '0'. Karena Q0 di sini memasukkan input clock dari flip-flop berikutnya, FF1 flip-flop juga beralih. Jadi, Q1 beralih dari '0' ke '1'. Karena sandal jepit FF2 dan FF3 juga dibukukan dari keluaran pelengkap sandal jepit mereka sebelumnya, mereka juga beralih. Dengan demikian, penghitung bergerak dari kondisi 0000 ke kondisi 1111 dengan pulsa clock pertama. Dengan pulsa clock kedua, Q0 beralih lagi, tetapi flip-flop lainnya tetap tidak terpengaruh karena alasan yang jelas dan penghitung berada dalam kondisi 1110. Dengan pulsa clock berikutnya, penghitung terus menghitung ke bawah oleh satu LSB pada satu waktu sampai mencapai 0000 lagi, setelah itu proses berulang. Urutan penghitungan diberikan sebagai 0000, 1111, 1110, 1101.1100, 1011, 1010, 1001, 1000, 0111, 0110, 0101, 0100, 0011, 0010, 0001 dan 0000. Bentuk waktu ditunjukkan pada Gambar 11.8. Jadi, kami memiliki penghitung empat bit yang diperhitungkan dalam urutan terbalik, dimulai dengan penghitungan maksimum. Ini adalah penghitung BAWAH

5. Video[kembali]

11.2

11.3

11.4

11.5

11.6

11.7

6. Link Download

[kembali]

Rangkaian

Download rangkaian 1 disiniDownload rangkaian 2 disini.

Download rangkaian 3 disini.

Download rangkaian 4 disini.

Download rangkaian 5 disini.

Download rangkaian 6 disini.

Video

Download video rangkaian 1disini.

Download video rangkaian 2 disini.

Download video rangkaian 3 disini.

Download video rangkaian 4 disini.

Download video rangkaian 5 disini,

Download video rangkaian 6 disini.

Download HTML disini.

Download datasheet JK-flip flop disini.

Download datasheet NAND gate disini.

Tidak ada komentar:

Posting Komentar